## Small signal analysis of two stage operational amplifier on TSMC 180nm CMOS technology with low power dissipation

Jahid khan<sup>1</sup> Ravi pandit<sup>1</sup>

<sup>1</sup>Department of Electronics & Communication Engineering, <sup>1</sup>Oriental University, Indore, M.P., INDIA 453331

**Abstract** :In this paper a low voltage two stage Cc miller compensated operational amplifier design is proposed and implemented using 0.18 $\mu$  micron CMOS process. It discusses low power dissipation (P<sub>Diss</sub>) 0.64mV and gain (A<sub>V</sub>) 70dB, exhibits a Unity Gain Frequency (UGF) of 3.2599 MHz, phase margin 83.07° and Gain margin 57dB. The design has been carried out in Tanner Tool v14.1 BSIM3v31 model library, Berkeley BSIM3 VERSION 3.1.

Key Terms: Two stage operational amplifier, small signal analysis, AC Analysis, Slew rate, CMOS technology, Miller compensated op-amp, Phase margin Gain margin, Gain Bandwidth, power dissipation.

#### **1. Introduction**

In current uses of most of consumers, industrial and scientific devices operational amplifier uses very large scale of array. Op-amp architectures that use two or more gain stages [1] are widely used when higher gains are needed. Op-amps are available in many topologies a two stage Opamp is one of them which is used for high gain amplification [2].

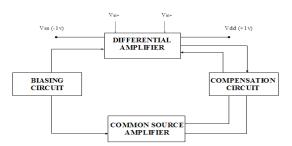

# 2.Block diagram of proposed two stage operational amplifier and operation

The W/L ratios of the transistors are chosen based on the saturation region operation. The first aspect ratios (W/L) of transistors are calculated using the saturation region current equation  $I_D[1][2][4]$ .

$$I_{D} = \beta \left[ (V_{gs} - V_{th}) - (V_{ds}/2) \right] V_{ds}$$

(1)

Figure 1 Proposed block of diagram of two stage Opamp

Where  $I_D$  is Drain current which is taken as the biasing current,  $\beta$  is the process parameters, (W/L) is the aspect ratio of a transistor,  $V_{gs}$  is Gate source voltage,  $V_{th}$  is Threshold voltage.  $V_{ds}$  is Drain to Source voltage Table 1: Modeling of proposed two stage op-amp

| Sn | Parameter                             | Uni<br>t | Main Results             |

|----|---------------------------------------|----------|--------------------------|

| 01 | Compensation capacitor<br>(Cc)        | pF       | 2.9 ≈ <b>3</b> pF        |

| 02 | Load capacitor (C <sub>L</sub> )      | pF       | 10 pF                    |

| 03 | Total Drain Current(I <sub>DD</sub> ) | μA       | 14.31×10 <sup>-6</sup> A |

| 04 | Tail current (I <sub>5</sub> )        | μA       | 14.31µA                  |

| 05 | W/L ratio of first<br>andsecondCMOS   | μs       | 2.9 ≈ <b>3 μs</b>        |

| 06 | W/L ratio of first<br>andsecondCMOS   | μs       | 2.058 <b>µs</b>          |

ISSN:2319-7900

| 07 | Tranconductance (g <sub>m</sub> )for<br>MM1and MM2CMOS                              | μs      | 1.8455 <b>µs</b>          |

|----|-------------------------------------------------------------------------------------|---------|---------------------------|

| 08 | Saturationvoltage(Dra<br>into source voltage)for<br>MM1 CMOS                        | mV      | 888.9×10 <sup>-3</sup> mV |

| 09 | Saturation voltage (Drain<br>to source voltage) for<br>MM5 CMOS<br>transistor(VDS5) | mV      | 4.89mV≈5mV                |

| 10 | Gain Bandwidth (GB)                                                                 | Mh<br>z | 6Mhz                      |

|    |                                                                                     |         |                           |

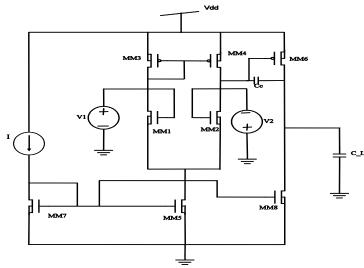

Figure 2 circuit diagram of propose two stage operational amplifier.

# **3.**Propose circuit diagram of two stage **Op-amp**

For congenital simply define notation  $s_i = (W/L)_i$ Where  $s_i$  is aspect ratio of a transistor. We are assume here  $g_{m1}=g_{m2}=g_{m1}$  and  $g_{m6}=g_{m11}$ . For first step of operational amplifier is to calculate the minimum value of the compensation capacitor  $C_C$ , We know that placing the output pole  $P_2$  2.2 times higher than the GB(Gain Bandwidth) permitted a 83.07° phase margin (assuming that the RHP zero  $Z_1$  is placed at or beyond ten times GB)[3][4]. It was shown that such pole and zero placements result in the following requirement for the minimum value for Cc:

Next we need to determine the minimum value for the tail current  $I_5$ , based on slew-rate requirements. as know as show in Fig(b) the  $I_{dis}$  is the drain to source current when the CMOS transistor in saturation region and we know very well that  $I_{dis}$  is equal to the summation of  $I_{D1}$  and  $I_{D2}$  drain to source current which is flow between drain to source when the both CMOS transistor in the saturation region across the MM1 and MM2 transistor so the total amount of  $I_{DD}$  is equal to the  $I_{DD} = I_{D1} + I_{D2}$  (3)

$$I_{D1} = \beta_1 [(V_{gs1} - V_{th1}) - (V_{ds1}/2)] V_{ds1}$$

(4)

$$I_{D2} = \beta_2 [(V_{gs2} - V_{th2}) - (V_{ds2}/2)] V_{ds2}$$

(5)

$Cc = 0.22 X C_{L}$

So the total amount of  $I_{DD}$  will be summation of  $I_{D1}$  and  $I_{D2}$ .

#### 3.1 Slew Rate

Slew rate can only occur when the differential input signal is large enough to cause *ISS* (*IDD*) to flow through only one of the differential input transistors.[2]

$$SR = \frac{ISS}{CL} = \frac{IDD}{CL}$$

(6)

Then the tail current will be  $I_5 = SR \times C_C$

The aspect ratio of MM3 CMOS Transistor can now determined by using the requirement for positive input common-mode range.

$$S3 = (W/L)3$$

$$= \frac{I5}{K'[VDD - Vin(max) - VOT03max + VTmax]}$$

$$S3 = \left(\frac{W}{L}\right)3$$

$$S_3 = S_4 \tag{8}$$

The transconductance of the input Cmos transistor can be determine with the help of  $V_{DS1}$ (Drain to source voltage of MM1 Transistor) and  $\beta_1$ (The process parameters of MM1 Transistor) and represented by as [4][3]:

$$g_{m1} = \beta_1 \times V_{DS1} \tag{9}$$

34

ISSN:2319-7900

The MM1 CMOS transistor ratio

$$(W/L)_1$$

is directly calculated from  $g_{m1}$  which shown below:  $S_1 = (W/L)_1 = \frac{gm1}{gm1} = S_2$  (10)

$\frac{1}{1} \frac{1}{15}$ Here are enough information available to calculate the saturation voltage of transistor MM5

$V_{DS5}=V_{in(min)}-V_{ss}-\sqrt{\frac{r_{5}}{\beta}}-V_{T1(max)}$  (11) With the help of  $V_{DSS}$  we can determined, (W/L)5 be extracted using the following way :

$$S_5 = \frac{IS}{K'(VDS5)^2}$$

(12)

Here the first stage of operational amplifier is complited.Next stage is output stage of operational amplifier. For the phase margin of 45.18dB, the location of the output pole was considered to be placed at 2.2 times the gain Bandwidth (GB) then Zero placed at least ten times higher than the GB. [3][4]The transconductance  $g_{m6}$  can be determined using

$$g_{m6} = 10 gm_1$$

(13)

for determination of Phase margin , the value of  $g_{m6}$  is approximately Ten times the input stage transconductance  $g_{m1}$  on this stage two possible approaches to completing the design of MM6.[4][5]Figure of Merit of MOS Transistors can be determine by

$GB = g_{m1}/C_c = 6Mhz$

As we know that in the Fig(b),the first stage is to achieve proper mirroring of the first stage current mirror load of MM3 and MM4 CMOS Transistor and this requires that [5]:

$V_{GS4} = V_{GS6} \qquad (14)$ Assuming  $g_{m6} = 11.3 \ \mu s$  and calculating  $g_{m4}$  as :

$g_{m6} = 10 \times GB \times Cc$  $g_{m6} = 6 \times 10^{-12}$

Knowing  $g_{m6}$  and  $s_6$  will define the Dc current  $I_6$  using the following equation:

$$I_6 = gm_6^2 / 2 \times (k_6') (W/L)_6 = 1.08 \mu A$$

(15)

The device size of  $MM_7$  can be determined from the balance equation given below:

$$S_7 = (W/L)_7 = (W/L)_5 \times \frac{16}{15}$$

(16)

Let's us check the Vmin (out) although the W/L of  $MM_7$  is large enough that this is probably not necessary. The value of Vmin (out) is

$$V_{\min(out)} = V_{DS7(sat)} = \sqrt{\frac{2 \times I6}{K \times 57}}$$

(17)

$V_{min(out)} = 1.11690 \mu V$ , which is less than required, At this point, the first stage-cut design is completed. Gain margin and Phase Margin [6] :

$$\frac{2 \times gm2 \times gm6}{PM = I5 \times (\lambda 2 + \lambda 3) \times (\lambda 6 + \lambda 7)}$$

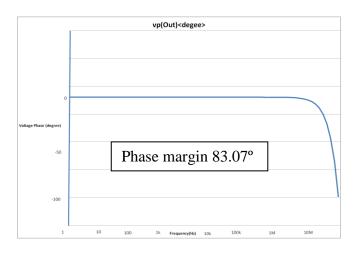

PM = 83.07°

(18)

Here gm2 and gm6 are transconductances of CMOS transistor  $MM_2$  and  $MM_6$  and  $\lambda_2$ ,  $\lambda_3$ ,  $\lambda_6$ ,  $\lambda_7$  are different channel length modulation for n-channel as well as p-channel.

#### **4** Power Dissipation

$$P_{\text{Diss}} = (I_6 + I_5) (V_{\text{DD}} - V_{\text{SS}})$$

(19)

Table : 2 Aspect Ratios of the Transistors  $(W/L)\mu m$  for the Two Stage Compensated Op-Amp.

| Transistor | Aspect Ratios (W/L)µm   |

|------------|-------------------------|

| MM1        | 1/0.18µm = 5.55         |

| MM2        | 1/0.18µm = 5.55         |

| MM3        | <b>1.8/0.18 μm</b> = 10 |

| MM4        | <b>1.8/0.18 μm</b> = 10 |

| MM5        | 3.5/0.18 μm= 19.44      |

| MM6        | 6/0.18 μm= 27.44        |

| MM7        | 3.5/0.18µm= 19.44       |

| MM8        | 4.5/0.18 μm=25          |

5. Implemented Results

The two stage op-amp is simulated using the  $0.18\mu$ m CMOS technology. The transient analysis for the op-amp circuit is taken for 1V p-p differential voltage and Gain Bandwidth 6 MHz.

The phase margin analysis of the two stage op-amp circuit is shown in figure(c).

#### 4.1 A. C. Analysis

Phase Margin: Phase margin of proposed Op-amp is 83.07°.

Figure 3 Phase Margin of two stage Op-amp

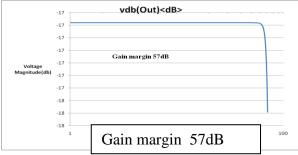

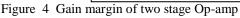

Gain Margin : Gain margin of proposed two stage Op-amp is 57dB.

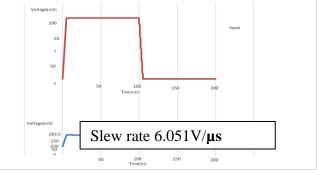

5.2 Slew Rate analysis

Slew rate of proposed Op-amp is 6.051V/µs

Figure 5 Slew Rate of two stage op-amp

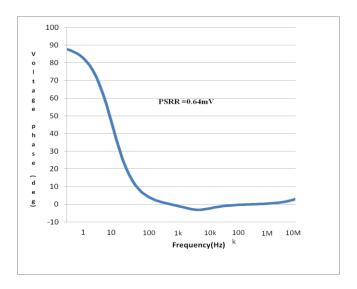

5.3 PSRR (Power Supply Rejection Ratio) Power Supply Rejection Ratio of proposed op-amp is

Power Supply Rejection Ratio of proposed op-amp is 0.64mV.

Figure 6 PSRR of two stage op-amp

Table 3 Performance Summary of the Op-Amps

| Parameters       | Performance on the bases of |

|------------------|-----------------------------|

|                  | 0.18µm CMOS Technology      |

| Gain (dB)        | 70dB                        |

|                  |                             |

| Gain margin (dB) | 45dB                        |

|                  |                             |

| Phase Margin (°) | 83.07°                      |

|                  |                             |

ISSN:2319-7900

| Bandwidth (MHz)                   | 7.565Mhz   |

|-----------------------------------|------------|

| Power Dissipation                 | 15.39mwatt |

| Power Supply Rejection Ratio (mV) | 0.64mV     |

| Slew Rate (V/ µs)                 | 6.051V/µs  |

#### Conclusions

Two stage operational amplifier using  $0.18\mu$  CMOS technology on Millers compensation capacitor (Cc) with 10kohm Register (R) with parallel based on compensation of right half plane Zero. A carefully and wide analysis are required to get good exertion and desired results. The gain Bandwidth (GB) which is a constant make remonstrance to the designing the circuits for high DC gain and high bandwidth applications. The improvement in unity gain bandwidth has been done by increasing the bias current up to 14.31µamp which decreases the DC gain and increases the power dissipation at the 0.64mv, still provides a good alternative control for an operational amplifier to operate at a high frequency avoid the white noise and short noise which is occur with increasing resister (R) values.

#### 6.Acknowledgment

The authors would like to thank to Nand Kishor Yadav, Dean and research, Oriental University, Indore to give their valuable and technical suggestion to encourage this Research.

#### 7. References

[1]Behzad Razavi, Design of Analog CMOS Integrated circuits, McGraw-Hill Company, New York, 2001.Page 167

[2]Allen holberg CMOS Analog Circuit Design, 2nd Edition©P.E.Allen-2010Page75,Page251,Page254,Page255,Page260.

[3]R. Jacob Baker, Harry W. Li and David E. Boyce, "CMOS Circuit Design, Layout and Simulation,"IEEE Press Series on Microelectronic Systems.Page265, Page254 [4] Phillip E. Allen and Douglas R. Holberg CMOS analog circuit Design, II edition, Oxford University Press, New York 2002. Page269 Page270, Page271, Page272, Page273

[5]Ankit Kapil, Arpan Shah, Rekha Agarwal, Sandhya Sharma "Analysis and Comparative Study of Different Parameters of Operational Amplifier Using Bipolar Junction Transistor and Complementary Metal Oxide Semiconductor Using Tanner Tools," International Journal of Soft Computing and Engineering (IJSCE) ISSN: 2231-2307, Volume-2, Issue-5, November 2012.

[6] Chaithra T S1 Ashwini2 Assistant Professor ECE 2Dept of Electronics and Communication PESIT, Bangalore, Karnataka, India "IOSR Journal of Electronics and Communication Engineering (IOSRJECE)" ISSN : 2278-2834 Volume 1, Issue 6 (July-Aug 2012), PP 39-45.

[7] Alan Hastings, *The Art of Analog Layout*, Prentice Hall, 2nd edition, 2005.